7.3 Structure and role of the processor part 1

## Q1.

#### All marks AO1 (understanding)

| Level | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        | Mark<br>Range  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 4     | A line of reasoning has been followed to produce<br>a coherent, relevant, substantiated and logically<br>structured response. The response covers all<br>three areas indicated in the guidance below and<br>in at least two of these areas there is sufficient<br>detail to show that the student has a good level<br>of understanding. To reach the top of this mark<br>range, a good level of understanding must be<br>shown of all three areas. | 10-12          |

| 3     | A line of reasoning has been followed to produce<br>a coherent, relevant, substantiated and logically<br>structured response which shows a good level of<br>understanding of at least two areas indicated in<br>the guidance below.                                                                                                                                                                                                                | 7-9            |

| 2     | A limited attempt has been made to follow a line<br>of reasoning and the response has a mostly<br>logical structure. At least four points have been<br>made. Either a good level of understanding of<br>one area from the guidance has been shown or<br>a limited understanding of two areas.                                                                                                                                                      | 4-6            |

| ΧA    | A few relevant points have been made but there<br>is no evidence that a line of reasoning has been<br>followed. The points may only relate to one or<br>two of the areas from the guidance or may be<br>made in a superficial way with little<br>substantiation.                                                                                                                                                                                   | <sup>1-3</sup> |

#### Guidance – Indicative Response

For each guidance point, if the student expands on the point to explain in what way the measure will improve performance then this can be considered to be a second point. For example:

- "Using a processor with more cores" is one point.

- "Using a processor with more cores which will be able to execute multiple instructions simultaneously" is two points.

Note that just "faster" is not enough to count as an expansion point without an explanation of why.

#### 1. Server Hardware

Replace the processor with one which has more cores

Replace the processor with one which has more cache memory // increase the

amount of cache memory

Replace the processor with one which runs at a faster clock speed **NE**. faster processor

Use a parallel processor architecture // use more processors which can work in parallel

Use a processor with a bigger word size

Use a processor that makes (better) use of pipelining

Install more RAM // main memory // primary memory

Use RAM // main memory // primary memory with a faster access time

Replace HDDs with SSDs // Replace HDDS with HDDs that can read data at a faster rate

Defragment the HDD

Replace the motherboard with one which has buses which run at a faster clock speed

Replace the motherboard with one which has more lines in the data bus

Use the Harvard architecture

Distribute the processing across multiple servers

#### 2. Network

Replace the network cable with cable that has a higher bandwidth // replace copper cable with fibre-optic cable **A.** Ethernet cable for fibre-optic NE. higher bandwidth network

Replace any wireless / WiFi connections with wired ones

Replace the network cards with ones that can transmit data at a higher bitrate

Consider the overall network design eg how the network is divided into subnets **A**. split the network into subnets

Use a star topology (instead of a bus)

Consider using a more efficient protocol for the data across the network

Add additional wireless access points

#### 3. Database and Software

Use a more efficient technique for controlling concurrent access to the database // replace record/table locks with serialisation/timestamp ordering/commitment ordering

Replace the database software with software that uses more efficient algorithms for tasks **A.** examples eg replace linear search with binary search

Use the index feature of the database to speed up searching on fields that are commonly used for this purpose

Rewrite the database software in a language that is suitable for concurrent execution // use a functional programming language for the database software

Ensure the software is compiled rather than executed by an interpreter // rewrite the software in assembly language/machine code

Review the conceptual model of the database to see if it contains any inefficiencies such as data redundancy that could be eliminated **A**. normalise the database design

Consider if it would be appropriate to sacrifice normalisation of the conceptual model to improve performance

Use a non-relational database system **A.** examples eg NoSQL

Distribute the data across multiple servers

Try to reduce the amount of other (unrelated) software that might be running on the database server at the same time

Try to reduce the number of database accesses that need to be made simultaneously // run some tasks at quiet times / overnight Purge / archive data that is no longer necessary / in use

[12]

## Q2.

(a) Marks are for AO3 (program)

#### Answer 1

- 1. ADD R0, R0, #1;

- 2. CMP R0, #11;

- 3. BNE; startloop;

#### Answer 2

- 1. ADD R0, R0, #1;

- 2. CMP R0, #11;

- 3. BEQ endloop;

- 4. B startloop ;

#### Answer 3

- 1. CMP R0, #10;

- 2. BEQ endloop ;

- 3. ADD R0, R0, #1;

- 4. B startloop ;

#### Answer 4

1. ADD R0, R0, #1;

#### 2. CMP R0, #11; RS PRACTICE 3. BLT; startloop ;

Stop marking when the first incorrect command is encountered. Mark response against whichever alternative gives the highest mark.

I. Any extra commands which do not effect operation of program.

#### Mark is for AO2 (apply) (b)

28<sub>10</sub> // (000)11100<sub>2</sub>;

TO. If two answers given and one is incorrect.

I. Lack of subscript.

[5]

1

4

#### Q3.

Mark is for AO1 (understanding)

Direct addressing means that the operand is the (memory) address/register number (of the datum) whereas immediate addressing means the operand is the datum :

**Note:** Must be clear that the operand is being used.

#### Q4.

#### Key points of subject criteria:

FETCH:

Contents of Program Counter/PC transferred to Memory Address Register/MAR: Address bus used to transfer this address to main memory; Contents of addressed memory location loaded into the Memory Buffer Register/MBR: Transfer of content uses the data bus; Increment contents of Program Counter/PC; Increment Program Counter/PC and fetch simultaneously; Transfer content of Memory Buffer Register/MBR to the Current Instruction Register/CIR;

A. Increment PC at any part of fetch process after transfer to MBR A. Reference to MDR (memory data register) instead of MAR

DECODE:

Decode instruction held by the Current Instruction Register/CIR; The control unit decodes the instruction: Instruction split into opcode and operand(s);

#### EXECUTE:

If necessary, data is fetched;

The opcode identifies the operation to be carried out by the processor; Execute instruction by relevant part of processor; Result stored in accumulator/ (destination) register;

If jump/branch instruction Program Counter/PC is updated;

#### Mark Bands and Description

| 7-8 | To achieve a mark in this band, candidates must meet the subject criterion (SUB) and all 5 of the quality of written communication criteria (QWCx).               |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | SUB Candidate has provided at least 7 points. At least one point made for each of the fetch, decode and execute stages. Answer must mention at least 3 registers. |

|     | QWC1 Text is legible.                                                                                                                                             |

|     | QWC2 There are few, if any, errors of spelling, punctuation and grammar. Meaning is clear.                                                                        |

|     | QWC3 The candidate has selected and used a form and style of writing appropriate to the purpose and has expressed ideas clearly and fluently.                     |

|     | QWC4 Sentences (and paragraphs) follow on from one another clearly and coherently.                                                                                |

|     | QWC5 Appropriate specialist vocabulary has been used.                                                                                                             |

| 4-6 | To achieve a mark in this band, candidates must meet the subject                                                                                                  |

|     | 1           |                                                                                                                            |

|-----|-------------|----------------------------------------------------------------------------------------------------------------------------|

|     |             | (SUB) and 4 of the 5 quality of written communication criteria                                                             |

|     | (QWCx).     |                                                                                                                            |

|     | SUB         | Candidate has provided at least 4 points covering at least 2                                                               |

|     |             | of the fetch, decode, execute stages. Answer must mention                                                                  |

|     |             | at least 2 registers.                                                                                                      |

|     | QWC1        | Text is legible.                                                                                                           |

|     | QWC2        | There may be occasional errors of spelling, punctuation and grammar. Meaning is clear.                                     |

|     | QWC3        | The candidate has, in the main, used a form and style of writing appropriate to the purpose, with occasional lapses.       |

|     |             | The candidate has expressed ideas clearly and reasonably fluently.                                                         |

|     | QWC4        | The candidate has used well-linked sentences (and                                                                          |

|     |             | paragraphs).                                                                                                               |

|     | QWC5        | Appropriate specialist vocabulary has been used.                                                                           |

| 1-3 |             | ve a mark in this band, candidates must meet the subject<br>(SUB) and 3 of the 5 quality of written communication criteria |

|     | SUB<br>QWC1 | Candidate has made a small number of relevant points.<br>Most of the text is legible.                                      |

|     | QWC2        | There may be some errors of spelling, punctuation and                                                                      |

|     |             | grammar but it should still be possible to understand most of the response.                                                |

|     | QWC3        | The candidate has used a form and style of writing which has<br>many deficiencies. Ideas are not always clearly expressed. |

|     | QWC4        | Sentences (and paragraphs) may not always be                                                                               |

|     |             | well-connected.                                                                                                            |

|     | QWC5        | Specialist vocabulary has been used inappropriately or not at all.                                                         |

| •   |             |                                                                                                                            |

| 0   | Candidat    | e has made no relevant points.                                                                                             |

## PAPERS PRACTICE

(a) Effective speed at which data can be retrieved will be increased; A. Larger "chunks" of data/instruction can be fetched in one operation

Max 1

1

(b) The amount of available memory locations / addressable locations will double; **NE**. increases amount of memory

[2]

## Q6.

#### (a) Marks are for AO1 (knowledge)

instructions are stored in main memory; instructions are fetched, (decoded) and executed by the processor; programs can be moved in and out of main memory; Max 2

MAX 2

2 marks for AO1 (knowledge) and 4 marks for AO1 (understanding) (b)

|     | Level  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 | Mark Range |       |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|

|     | 3      | A detailed description,<br>indicating a comprehensive<br>knowledge has been provided<br>which covers all three stages.<br>For each stage, the<br>description covers the majority<br>of the points listed in the<br>guidance. The answer is well<br>structured and points are<br>connected in a way that<br>demonstrates a good<br>understanding of the complete<br>cycle.                                                                   | 5 – 6      |       |

|     | 2      | An adequate description<br>indicating knowledge of the<br>cycle has been provided that<br>either covers one or two<br>stages in a good level of<br>detail, including the majority of<br>points for each stage, or<br>covers all three stages but at<br>a more superficial level. The<br>answer is satisfactorily<br>structured and points are<br>connected in a way that<br>demonstrates an<br>understanding of some parts<br>of the cycle. | 3-4        |       |

| EX/ | ۱<br>۱ | A small number of points, from<br>one or more stages have<br>been recalled indicating some<br>knowledge of the cycle.<br>However, these have not<br>been connected and<br>demonstrates little or no<br>understanding of any stage of<br>the cycle.                                                                                                                                                                                          |            | CTICE |

#### FETCH:

- contents of PC transferred to MAR

- address bus used to transfer this address to main memory

- contents of addressed memory location moved into the MBR

- transfer of content used the data bus

- increment PC

- transfer content of MBR to CIR.

#### DECODE:

- decode instruction held by the CIR

- the control unit decodes the instruction

- instruction split into opcode and operand.

EXECUTE:

- if necessary, data is fetched

- the opcode identifies the instruction to execute / operation to perform

6

1

1

2

- execute instruction by relevant part of processor

- result stored in accumulator

#### (c) Mark is for AO1 (knowledge)

**1 mark:** A language that is very similar to / based upon the instruction set of the computer;

#### (d) Mark is for AO1 (knowledge)

1 mark: (opcode) represents the instruction to be executed;

#### (e) 1 mark for AO1 (knowledge) and 1 mark for AO1 (understanding)

#### AO1 (knowledge):

**1 mark:** Immediate addressing: the operand value is part of the instruction / / no need to go to any memory address;

AO1 (understanding):

1 mark: Example:

MOV RX, #Y;

[where X is 0-12 and Y is a decimal value]

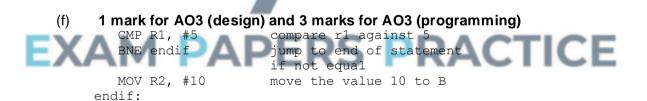

#### AO3 (design) – 1 mark:

**1 mark:** Identifying that a comparison and branch are required to have the same effect as the IF statement, even if the syntax or comparison made are incorrect

#### AO3 (programming) – 3 marks:

For the AO3 (programming) marks, the syntax used must be correct for the language as described on the question paper.

**1 mark:** Comparing R1 against 5 and having a branch with the correct logical condition

**1 mark:** For moving 10 to R2

1 mark: For having a label for end of statement (that is used in the branch)

I Load instruction to setup R1 from X.

4

1

3

#### Q7.

| (a) | operand;       |

|-----|----------------|

|     | R operand code |

- (b) (i) PC 0010; MAR 0001; MBR 00100100;

- (ii) The instruction is held in the CIR // instruction in CIR is decoded;

A IR

The control unit / instruction decoder decodes the instruction; **NE** the processor decodes the instruction

Instruction will be split into opcode and operand; **R** if it is implied that a register will do this splitting / decoding

Relevant part of processor / CPU executes instruction // using ALU to perform calculations; A instruction executed by the control unit / ALU NE processor executes instruction

Further memory fetches / saves carried out if required;

Result of computation stored in accumulator / register / written to main memory;

*By example:* Will ADD contents memory location 0100 to accumulator;

MAX 3

(c) The current value in the accumulator would be stored in (memory) address / location 0011 / 3;

Number 011 / 3 stored in (memory) address / location 0011 / 3;

MAX 1

#### Q8.

(a) increase the number of bits that can be transferred <u>at one time</u>;

A increase rate of data transfer;

increases the number of (memory) addresses / addressable locations / / increase the maximum amount of primary store / memory (possible);

|     | fetch | uctions performed more quickly / / instructions executed at faster rate / /<br>execute cycle will happen faster / /<br>ased heat may cause malfunctioning of device / / overheating;                                                           |       |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|     | A ca  | lculations / operations / commands for instructions                                                                                                                                                                                            | 3     |

| (b) | (i)   | a (hardware) device / component that is not part of the CPU;<br>NE processor / computer<br>a (hardware) device not directly under the control of the processor /<br>CPU;                                                                       |       |

|     |       | a device that communicates through an I / O controller;<br>external hardware / device;<br>R examples alone                                                                                                                                     |       |

|     |       |                                                                                                                                                                                                                                                | MAX 1 |

|     | (ii)  | to allow exchange of data / instructions / signals between the processor<br>and the peripheral;<br>A communicate<br>R information                                                                                                              |       |

|     |       | NE To allow the device to be connected                                                                                                                                                                                                         | 1     |

|     | (iii) | Electronics that interface the controller to the system bus;<br>Electronics appropriate for sending signals to the device connected to<br>the computer;                                                                                        |       |

|     | (iv)  | Each peripheral operates in a different way;<br>Not sensible to design a processor to control every possible peripheral;                                                                                                                       | MAX 1 |

|     |       | A new type of peripheral would require the processor to be redesigned;<br>Peripherals may operate at a different voltage from the processor;<br>Peripherals will usually operate at a slower rate than the processor<br>(requiring buffering); |       |

|     |       |                                                                                                                                                                                                                                                | MAX 2 |

| EX  | A     | M PAPERS PRACTICI                                                                                                                                                                                                                              | Ξ     |

- Q9.

- Program Counter / Sequence Control Register; Memory Address Register; Memory Buffer Register / Memory Data Register; Current Instruction Register; R Abbreviations

Max 2

[8]

(b) **Step 1:** MAR ← [PC] / Contents of program counter transferred to MAR;

$\mathbf{R}$  MAR  $\leftarrow$  PC

**R** [MAR] ← PC (see note about **DPT**) **R** PC sends / transfers

**Step 2b:** MBR ← [Memory]<sub>addressed</sub> / Contents of addressed memory location loaded into MBR; (must have concept of data coming from address in memory, not just going into MBR)

Step 4: Decode instruction;

A Contents of CIR decoded A Instruction is split into opcode and operand R Data for instruction R CIR decoded, CIR decodes instruction Note: A. [CIR] decoded

1 mark for each correct step

For PC accept Program Counter / SCR / Sequence Control Register For MAR accept Memory Address Register For MBR accept Memory Buffer Register / MDR / Memory Data Register

A Other means of indicating transfer e.g. [PC] →

MAR

A [Memory] for [Memory]<sub>addressed</sub>

DPT – no / incorrect square bracket use for register transfer notation

#### Q10.

- (a) A set of rules / regulations (to allow communication between devices) // set of agreed signals / codes for data exchange;

NE a rule // a regulation // a signal // a code

NE instruction(s)

- (b) Analyses statement by statement each line of source code

A runs / translates / executes line by line

R compiles (line by line)

Calls routines to carry out each instruction / statement

Max 2

3

1

[5]

(c) Instructions / programs stored (with data) in main memory; A memory // RAM

Program run by fetching, (decoding and executing) <u>instructions</u> (from main memory)\* in sequence;

Program can be replaced by loading another program into (main) memory

Contents of a (main) memory location can be interpreted as either an instruction or data;

\* = This mark can be awarded without the explicit reference to main memory if main memory has already been mentioned elsewhere in the response.

Otherwise, the answer must make clear that the instructions are coming from the main memory to get this mark.

3

(d) LOAD 21 STORE 23

> LOAD 22 STORE 21

LOAD 23

#### STORE 22

mark for value from 21 stored into 23;

mark for value from 22 being moved to 21;

mark for value from 23 being moved to 22;

#### Alternative :

LOAD 22 STORE 23

LOAD 21 STORE 22

LOAD 23 STORE 21

mark for value from 22 stored into 23;

mark for value from 21 being moved to 22;

mark for value from 23 being moved to 21;

DPT if a different temporary storage area is used

I end of statement separators

Max 2 if the program does not fully work

Robots find it hard to adapt to changes in environment // Robots are unable to adapt to changes easily;

Robots find it hard to work with 3D vision;

Robots find it hard to detect edges between similar objects // robots find it hard to perform shape detection;

Robots find it hard to get feedback when gripping items;

Robots have limited processing power // too many variables to deal with;

Programming for vision/grip is a complex problem; A child builds up experience of using touch / vision;

A Robot cannot recognise when it makes mistakes;A Robot can't think for themselves // can't perform lateral thinking

Max 3

3

(f) (i) (Lens focuses) light / photons onto image sensor;**R** if uses 'reflection'

Image sensor is a CMOS / CCD / photoelectric device; CCD used ADC to convert measurement of light intensity into binary; CMOS uses transistors to generate binary value; Image sensor converts light into discrete / electrical signals / binary;

Image is captured when the shutter is pressed; Large pixels collect more electrons than small pixels and so produce better quality images; Firmware performs data processing to "tidy up" image; (Colour) filter used to generate data separately for Red, Green, Blue colour components; Aperture / shutter speed can be adjusted to cope with varying lighting conditions; Image is recorded as group / array of pixels // Image sensor consists of array of pixel (sensors)//etched into the image sensor's silicon are pixels;

Image data transferred to robot; Image data usually stored on solid-state disk;

Max 3

(ii) Robot has a low powered microprocessor;

Too much image data for the robot to process quickly // smaller resolution can be processed quicker;

A high resolution image has too much image data for the robot to store // low resolution uses less storage space;

Do not need high resolution to determine colour of balls;

**NE** allows more images to be stored

## Q11.

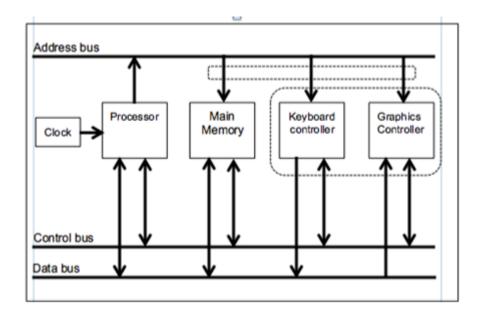

(a) A set of / group of / parallel wires / lines;

Wires needs to be qualified with set / group

that are used to connect together components (inside the computer) // connect different parts of the CPU

## in order to pass signals between them; R a wire

A connect different parts of the computer **NE** data

Max 2

2

(b) Instructions;

A Commands / machine-code

R signals

**Examples of a control signal (Max 1): NE** an event that details when an interrupt would be caused

Clock / timing; reset; interrupt ACK; interrupt request; bus grant; bus request; status; I / O write; I / O read; memory read; memory write; transfer ACK A interrupt A transfer request A read / write NE load / store NE clock speed

1 mark – one of processor, keyboard controller or graphics controller identified correctly 2 marks – all three correctly identified

Address bus connects the 4 components; Arrow from processor to the address bus; Arrows from address bus to the three other components;

Mark this on where the candidate has put the components.

#### Q12.

- (a) (i) Indicates the basic machine operation / function / command; Executable binary code;

A "instruction" – with a valid example

- (ii) Represents a single item of (binary) data / a single value; Represents a memory address / storage location; The value that the instruction operates on; A parameter for the operation NE "address"

Max 1

Max 1

5

[9]

(b) Easier to understand; Takes less time to code (as using mnemonic opcodes and hex operands); Fewer mistakes made in coding; Ability to add comments to code; Use of symbolic names for operands // easier to remember opcodes / mnemonics; Use of labels; Easier to maintain / debug; NE easier to read / code / write NE quicker A converse points if clearly discussing machine code

[4]

## Q13.

Key points of subject criteria:

#### Fetch:

Contents of Program Counter / PC transferred to Memory Address Register / MAR; Address bus used to transfer this address to main memory;

Contents of addressed memory location loaded into the Memory Buffer Register / MBR;

Transfer of content uses the data bus;

Increment contents of Program Counter / PC;

Increment Program Counter / PC and fetch simultaneously; A any part of fetch process

Transfer content of Memory Buffer

Register / MBR to the Current Instruction Register / CIR

#### Decode:

Decode instruction held by the Current Instruction Register / CIR; The control unit decodes the instruction; Instruction split into opcode and operand;

#### Execute:

| If necessary, data is fe | etched;          |                      |              | _     |

|--------------------------|------------------|----------------------|--------------|-------|

| The opcode identifies    | the type of ins  | tructio              | on it is;    |       |

| Execute instruction by   | relevant part of | of p <mark>ro</mark> | cessor;      |       |

| Result stored in accur   | nulator;         |                      |              |       |

| Status register update   | d;               |                      |              |       |

| If jump / branch instruc | ction Program    | Coun                 | ter/PC is up | dated |

To achieve a mark in this band, a candidate must meet the subject criterion (SUB) and 4 of the 5 quality of language criteria (QLx).

SUB Candidate has provided at least 6 points. At least one point made for each of the fetch, decode and execute stages. Answer must mention at least 3

registers. Text is legible.

- QL2 There are few, if any, errors of spelling, punctuation and grammar. Meaning is clear.

- QL3 The candidate has selected and used a form and style of writing appropriate to the purpose and has expressed ideas clearly and fluently.

- QL4 Sentences and paragraphs follow on from one another clearly and coherently.

- QL5 Appropriate specialist vocabulary has been used.

6

To achieve a mark in this band, candidates must meet the subject criterion (SUB) and 4 of the 5 quality of language criteria (QLx).

- SUB Candidate has provided at least 4 points covering at least 2 of the fetch, decode, execute stages. Answer must mention at least 2 registers

- QL1 Text is legible.

- QL2 There may be occasional errors of spelling, punctuation and grammar. Meaning is clear.

- QL3 The candidate has, in the main, used a form and style of writing appropriate to the purpose, with occasional lapses. The candidate has expressed ideas clearly and reasonably fluently.

- QL4 The candidate has used well-linked sentences and paragraphs.

- QL5 Appropriate specialist vocabulary has been used.

To achieve a mark in this band, candidates must meet the subject criterion (SUB). The quality of language should be typified by the QLx statements.

- SUB Candidate has provided at least one valid point.

- QL1 Most of the text is legible.

- QL2 There may be some errors of spelling, punctuation and grammar but it should still be possible to understand most of the response.

- QL3 The candidate has used a form and style of writing which has many deficiencies. Ideas are not always clearly expressed.

- QL4 Sentences and paragraphs may not always be well-connected or bullet points may have been used.

- QL5 Specialist vocabulary has been used inappropriately or not at all.

1–3

0

4–5

Candidate has not made reference to any of the points above.

[6]

#### Q14.

- (a) Third (generation) // 3; R High Level Language Do not reject high level language if answer also contains '3rd generation' refer upwards for anything else. 1 (b) Hexadecimal // base 16; (i) A Hex Hex used in textbook 1 ACTICE Take up less space when printing / viewing; (ii) NE takes up less space Less likely to make errors; Op-codes are easier to recognize; Easier to understand; Less time taken when coding as more concise // quicker to program; **NE** easier to read **NE** quick to write Max 1 Lowest address : 00 (iii) Highest address : FF BOTH correct to gain one mark; A 0 for lowest address A 255 for highest address A notation in front of hex &, \$ 1

- (c) When coding for execution speed;When coding to minimize object code size;

When writing code to control devices / directly access hardware; **A** When coding for a specific processor; **A** by example if maps to one of the above

(d) A compiler produces object code/machine code; whilst an interpreter does not produce any object code; Interpreted code will execute slower; than executing the object code produced by a compiler; You always need the interpreter to interpret source code; but you do not need the compiler to execute a compiled program; Once compiled source code is no longer required to run the program; An interpreter always needs source code at runtime; Compiled code can only be executed on a machine with the same processor type / instruction set; Interpreted code is more portable; A compiler translates the whole source code (at once); An interpreter analyses the code line by line; NE reads

1

1

Max 1

| Q15.<br>(a) |        |                             |   |

|-------------|--------|-----------------------------|---|

|             | Number | Component                   |   |

|             | 1      | Memory address<br>register; |   |

|             |        | NE MAR;                     |   |

|             | 2      | Data bus;                   |   |

| EX          | AM F   |                             | 3 |

- (b) To fetch / decode / execute instructions; To synchronise operation of processor; To marshal/control operation of fetch-execute cycle; To send control signals/commands to other components of fetch-execute cycle; To control the transfer of data between registers/MBR; A by example NE information

- Arithmetic (and) logic unit;

NE Arithmetic unit

NE Logic unit

~ 4 E

- (d) A (very fast) memory location within the processor;

A A (very fast) memory location within an I/O controller;

- (e) Arithmetic results Overflow/underflow/positive/negative/zero/carry;

Interrupts (enabled/disabled); Parity; BCD arithmetic enabled/disabled; Supervisor mode; Halt; **A** illegal instruction/operation Refer to team leader with other potentially correct answers.

#### Q16.

(a) Second (generation);

A 2

R assembly code / language

Note: Adding "assembly" / "assembler" does not talk out a valid mark for second / 2

Max 1

1

1

2

1

5

1

[5]

[7]

- (b) (memory) Address / location / offset;

A line number

R instruction number

- (c) (y) Opcode / operation code;

A op-code

NE operation

(z) Operand;

### (d) Individual Instructions:

One to one / each assembly language instruction translates to one machine code instruction;

#### Programs:

Figure 1 assembly language equivalent of figure 2 // figure 2 machine code version of figure 1 // figure 2 is assembled version of figure 1; NE figure 2 "binary version" of figure 1 NE different generations of language

## Q17.

(a)

- 1 clock;

2 (Main) memory / IAS; A RAM R ROM

3 Control bus;

4 VDU controller / output controller; A controller for other named output device

5 Processor; R Central Processing Unit / CPU

- (b) Memory address register; **R** abbreviations

- (c) Memory buffer register / memory data register;

#### R abbreviations 1 (d) Address bus has 64 lines / tracks/ wires // there are 2 ^64 memory locations available: NE 64 bits wide, moves 64 bits of data 1 [8] Q18. (a) Address (bus); 1 (b) 1; **R** 33 1 (c) A – Visual display unit; A VDU B – Processor; R CPU C – (Main) memory; D – Keyboard; 4 [6] Q19. (a) Operand - 5 Opcode - LOAD; A binary value 101 with any number of preceding zeroes for the operand Both needed for the mark 1 (b) LOAD CE Both Add instructions for the mark - do not 3 ADD need to follow each other. STORE 21 The operands for LOAD and ADD can be in any order I an end of line indicator symbol e.g. ";" I comments explaining code I additional unnecessary commands R commands with a # or ( ) or [] in the operand A operands in binary A operands in binary and opcodes in binary, if candidate has provided a translation table A correct operands in hex if using & Max 2 if code would not produce correct result

3

#### Q20.

| (a) Numbe<br>r | Component Name                |

|----------------|-------------------------------|

| 1              | Memory Address Register       |

| 2              | Address Bus                   |

| 3              | Memory Data / Buffer Register |

| 4              | Data Bus                      |

(b) The instruction is held in the CIR;

#### A IR

(i)

Assembler:

The control unit / instruction decoder decodes the instruction; The opcode identifies the type of instruction it is; Relevant part of CPU / processor executes instruction; A ALU Further memory fetches / saves carried out if required; Result of computation stored in accumulator / register / written to main memory: Status register updated; If jump / branch instruction, PC is updated; A SCR

- (c) Can be displayed in less space; R takes up less space NE Easier to remember / learn / read / understand; Less error prone; ERS PRACTICE<sup>Max 1</sup>

- HLLs are problem oriented; (ii) HLL programs are portable // machine / platform independent ; English like keywords / commands/ syntax / code; **R** closer to English Less code required // less tedious to program // one to many mapping of HLL statements to machine code commands; Quicker/easier to understand / write / debug /learn / maintain code; **R** just quicker/easier HLLs offer extra features e.g. data types / structures // structured statements // local variables // parameters // named variables/constants; R procedures / modular A example of a data structure NE "extra features" without example Speed of execution not crucial for most tasks so faster execution of assembly language not required; Most computer systems have a lot of (main) memory / RAM so compact object code not essential; A converse points for Assembly Language

4

Max 3

1

3

[12]

#### Q21.

Program Counter;

A Sequence Control Register

R Next Instruction

Register

Current Instruction Register;

A Instruction Register

Memory Buffer Register;

A Memory Data Register

Memory Address Register;

Max 2

Max 2

Max 1

1

1

- (b) Address in MAR/address to fetch instruction from, sent down Address Bus to Main Memory;

R address in PC (program counter) Contents of address accessed in Main Memory;

A by implication if contents of address location referred to during data transfer Contents of address location//instruction//data passed down Data Bus into MBR/to processor;

A MDR instead of MBR A RAM for Main Memory

- (c) Order of execution unimportant/one step does not rely on prior completion of the other;

Steps carried out by different (hardware) devices/components;

A operations are independent

A operations use different registers

R using different buses

# EXAM PAPERS PRACTICE

## Q22.

(a) (i) LOAD = Opcode 4 = Operand

1 mark for both parts correct

- (ii) A storage/memory location in the processor;

A CPU

NE location in the processor

- (b) LOAD 12;

ADD 13; STORE 14; A operands 12 and 13 swapped around BUT NOT swapped opcodes A correct binary operands 12- 1100 13- 1101 14- 1110 A minor spelling errors in Opcode only P1 for use of # or other symbols with operand

3

## Q23.

| (a) | pictu | allest ;<br>re element // unit which can be drawn on screen //<br>essable / resolvable part / unit of a picture ;                                                                                                                                                                                                                                                                                                   | 2           |      |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------|

| (b) | (i)   | 0010 1010 ;                                                                                                                                                                                                                                                                                                                                                                                                         | 2           |      |

|     | (ii)  | 184 ;                                                                                                                                                                                                                                                                                                                                                                                                               | 1           |      |

| (c) | (i)   | pixels are stored as numbers // bit patterns / binary code // RGB bits ;                                                                                                                                                                                                                                                                                                                                            | 1           |      |

|     | (ii)  | 8 ; <b>A</b> 1 byte                                                                                                                                                                                                                                                                                                                                                                                                 | 1           |      |

| (d) | (i)   | <pre>drawing is made up of drawing <u>objects</u> // or by example e.g. drawing is<br/>made up of circle / rectangle / straight line / etc. (must give at least two<br/>example objects);<br/>different objects(A shapes) have a defined set of <u>properties</u> // or by<br/>example;<br/>objects are stored as drawing commands / drawing list;<br/>some properties use mathematical equations / formulae;</pre> | Max 2       |      |

|     | (ii)  | object type ; co-ordinates / location of the <u>centre</u> <b>R</b> centre (only) ; radius / diameter ; fill colour ; fill style ; line thickness ; line colour ; line style ; anything reasonable ; <b>R</b> colour (only) Pasition (only)                                                                                                                                                                         | In a second |      |

| EX  | A     | R colour (only) Position (only) PRACTICE                                                                                                                                                                                                                                                                                                                                                                            | Max 3       | [11] |

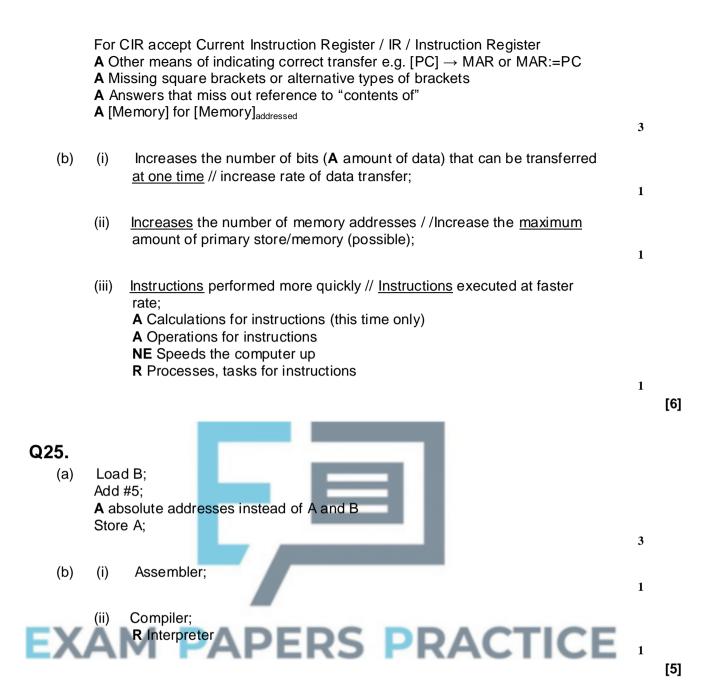

#### Q24.

(a) **Step 1**: MAR ←[PC] / Contents of program counter transferred to MAR;

**Step 2b:** MBR  $\leftarrow$  [Memory]<sub>addressed</sub> / Contents of addressed memory location loaded into MBR; (must have concept of data coming from address in memory, not just going into MBR)

Step 4: Decode instruction;A Contents of CIR decodedR Data for instructionR CIR decoded, CIR decodes instruction

1 mark for each correct step

For PC accept Program Counter / SCR / Sequence Control Register For MAR accept Memory Address Register For MBR accept Memory Buffer Register / MDR / Memory Data Register

#### Q26.

- 1. address of <u>next</u> instruction to be executed/fetched;

- 2. (contents of Program Counter) copied into Memory Address Register;

- Contents of <u>Program Counter</u> incremented (by 1);

A incrementing by more than 1

- 4. ...at the same time....; (only give a mark if between correct statements)

- 5. instruction/data held at that address is placed in the Memory Buffer Register;

- 6. Contents of Memory Buffer Register copied into Current Instruction Register;

- 7. Instruction held in Current Instruction Register is decoded;

- 8. If necessary data is fetched;

- 9. (and) instruction is executed by processor/ALU;

- 10. Address sent/transferred over address bus;

- 11. Data/instruction transferred to processor on data bus;

- 12. Result stored in accumulator;

Max 6

[6]

| Q27.                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |     |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|

| (a)                       | (memory) address / location;<br><b>R</b> Line number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |     |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1     |     |

| (b)                       | second (generation) //assembly language/code/program //<br>2 / 2 <sup>nd</sup> ;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |     |

|                           | 272,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1     |     |

| (c)                       | (i) assembl <u>er;</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |     |

|                           | R. assemb <u>ly</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1     |     |

|                           | (ii) orror list (orror roport (orror count ( <b>A</b> orror moscogo ( highlight                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |     |

|                           | <ul> <li>error list / error report / error count / A error message / highlight<br/>statement(s) illegally formed / instruction count // symbol table;</li> <li>R error</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |     |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1     |     |

| (d)<br><b>Q28.</b><br>(a) | program (instructions are) transferred from backing store to main memory;<br>program consists of a sequence of instructions;<br>stored in a (continuous area of) <u>main memory;</u><br>an <u>instruction</u> is fetched (and decoded);<br>and then <u>instruction</u> executed (by the processor);<br>program can be replaced by another program at any time;<br>program instructions are treated as data;<br>Need to access/address registers/exact memory addresses/ hardware<br>directly;<br>Fast speed of operation needed;<br>Code needs to take up little <u>memory</u> // minimise the size of the executable | Max 4 | [8] |

|                           | code;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -     |     |

| ΕX                        | A no compiler/interpreter exists yet for the machine// no other translator exis<br>R manipulate bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ts;   |     |

|                           | R comparison with machine code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |     |

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Max 2 |     |

| (b)                       | Takes longer to program;<br>Leads to more errors // more difficult to detect errors;<br>Requires more skill;<br>Difficult to understand;<br>Difficult to maintain;<br>Processor dependant// not portable// not problem oriented;                                                                                                                                                                                                                                                                                                                                                                                      | Max 1 | [3] |

| Q29.                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |     |

| (a)                       | <b>Processor/CPU;</b><br>Explanation faster execution of (program) <u>instructions</u> / the fetch-execute cyclis faster;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | le    |     |

**R** more 'calculations per second' Simultaneous processes possible / duel/quad – core processor;

#### Additional processor;

Processing is shared between two processors;

#### Graphics Card;

Explanation - increasing the speed at which images are rendered;

#### (main) memory / RAM;

Explanation – reduces main memory to disc transfers; Fit memory which has a faster read/write speed;

R Clock A Explanation – increasing the clock speed/over-clocking; R Cache A Explanation – program <u>instructions</u> are fetched faster from cache than main memory;

(b) Secondary storage/memory/disc store // (external) hard disk;

A HDD/ Hard drive Explanation – the storage space/capacity is increased;

**R:** 'bigger hard drive' or similar

## (c) Hub device / USB ports;

Card with additional serial /parallel ports / PCMCIA / USB ports; R Card with additional I/O ports Explanation – will allow/support the <u>simultaneous</u> connection of several devices;

#### Q30.

- (a) (i) 1 GB ;

- (ii) 300 GB PAPERS PRACTICE 1 (b) Control (bus);

- (c) Data bus has to transport data values to <u>and</u> from <u>various devices</u> /internal components;

Only the processor assigns address values to the different devices;

- (d) Logical // read // write // jump/branch // input // output // data transfer ;

A Boolean

- Program instructions are transferred from backing store to main memory ; Program consists of a sequence of instructions ; Program is stored in <u>main memory</u>; and can be replaced by another program at any time ; <u>Instructions</u> are fetched (in sequence) ; Decoded ; and then executed ;

Max 3

2

Max 2

1

1

1

[6]

## Q31.

- (a) To perform mathematical operations/calculations;

- (b) Fetches, decodes and executes instructions; To control/co-ordinate the other parts of the processor;

- Accumulator; Index Register; Base Register; Stack Pointer; Current Instruction Register; A Instruction Register Program Counter/ Instruction Pointer/ Sequence Control Register; <u>Memory</u> Address Register; <u>Memory</u> Data Register// <u>Memory</u> Buffer Register; Flags Register// Status Register// Condition Code Register; Interrupt Register;

Max 3

#### Q32.

|   | Component            | Name                                                                                                                      |

|---|----------------------|---------------------------------------------------------------------------------------------------------------------------|

|   | 1                    | Program Counter                                                                                                           |

|   | 2                    | Memory Address Register; A MAR                                                                                            |

|   | 3                    | Address Bus;                                                                                                              |

|   | 4                    | Data Bus;                                                                                                                 |

| E | 5<br><b>XAM</b><br>6 | Memory Data Register/ Memory Buffer Register; A<br>MDR/MBR<br>Current Instruction Register; A Instruction Register/IR/CIR |

#### Q33.

- (a) Halve the time to perform an operation; **A** Operations performed more quickly;

- (b) Increase the number of bits transferred at any one time from 16 to 32// Double the number of bits transferred at any one time;

- (c) Increase the number of memory addresses; from  $2^{24}$  to  $2^{32}$ ;

[4]

[5]

#### Q34.

(a) Assembly language/code/program // second (generation);

1

1

1

2

1

Max 1

|    | (b)        | Machi                            | ine code // first (generation);                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 |      |

|----|------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|

|    | (c)        |                                  | ory) address / location;<br>e number                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1 |      |

|    | (d)        | Asser                            | nbler;                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 |      |

|    |            |                                  | (mapping between instructions/op code/numbers written in assembler<br>eir machine code equivalent) / each assembly instruction translates into<br>achine code instruction                                                                                                                                                                                                                                                                                                         | 1 |      |

|    | (f)        |                                  | / error list / error report / error count / highlight statement(s) illegally<br>d // / instruction count // symbol table;                                                                                                                                                                                                                                                                                                                                                         | 1 | [6]  |

| 01 | 35.        |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |      |

| 4. | (a)<br>(b) | Instruc<br>Memo<br>Penali<br>(i) | am Counter; Sequence Control Register/Instruction Pointer<br>ction Register// Current Instruction Register;<br>ry Buffer Register// Memory Data Register;<br>ry Address Register;<br>se initials once only<br>Test for an interrupt/ check priority of interrupt<br>Identify the <u>source</u> of the interrupt;<br>Save and/or restore the volatile environment/registers;<br><u>Service</u> the interrupt; <u>A</u> handle the interrupt<br>Disable (lower priority) interrupts | 4 |      |

| E  | X          |                                  | Max 2 PAPERS PRACTICE Placed between Execute and Fetch; A before Fetch/ after execute <u>R</u> at end of cycle                                                                                                                                                                                                                                                                                                                                                                    | 2 |      |

|    | (c)        |                                  | <u>Interrupting</u> device/ source supplies;<br>An offset/vector;<br>A index/indexed address added to the <u>base address;</u><br>A <u>base</u> register                                                                                                                                                                                                                                                                                                                          |   |      |

|    |            |                                  | Gives the <u>start address</u> of interrupt service routine/ ISR//<br>Address vector table cell contains <u>start address</u> of ISR/<br><b>R</b> Interrupting device supplies <u>start address</u> of ISR                                                                                                                                                                                                                                                                        | 3 |      |

|    |            |                                  | A different <u>routine</u> can be easily introduced// <u>routine</u> can be relocated/<br>dynamically loaded; <i>or words to this effect</i><br><b>A</b> The interrupting device only needs to supply a new offset                                                                                                                                                                                                                                                                | 1 | [11] |

## Examiner reports

## Q1.

A very good range of responses was received to this question, with approximately half of students achieving five or more marks. Most students addressed all three aspects of the question (hardware, network, database and software). Students tended to make more points about how the hardware could be improved than about the other two areas. This was acceptable but students needed to have covered all three areas to achieve a mark of ten or above.

Some students wrote too vaguely to achieve marks, for example by writing that a "faster processor" would improve performance, without referencing a factor such as the clock speed that would make the processor faster. Other mistakes included believing that the question required students to contrast thin-client and thick-client and that the system was web based.

A small number of students wrote about issues which might be causing the system to perform poorly instead of explaining how the performance of the system could be improved. Such responses were not worthy of a mark.

## Q2.

(a) Answers to the assembly code question were generally better than the previous series, although more than half of students were not able to secure a mark. It was pleasing to see that previous advice has been heeded as far fewer students were using terminology that can be identified from the Little Man Computer, with the majority having instructions which were obviously AQA assembly code. Most commonly low-end marks were lost due to incorrect syntax – missing a comma In the ADD instruction is enough to lose the mark as syntactic correctness is essential. Whilst most students that scored well identified that a comparison was needed, getting the correct value for the comparison (#10 or #11) combined with the correct termination criterion proved harder and students are encouraged to work through a number of practical tasks using a simulator if possible.

A good number of students were able to provide a correct answer to this question. Although the answer was intended to be in denary, binary answers were not precluded in this question so either received the mark. Students should not rely on this in future series and should be able to answer in either base.

The most common mistake was 700, indicating the student was aware of what a shift was, but not the correct way to implement this.

## Q3.

Whilst many students showed some understanding on this question, it was quite common for the mark to be dropped when it wasn't clear that they were referring to the operand. "Immediate addressing uses a value whereas direct addressing uses a memory address" is insufficient while "Immediate addressing uses the operand as a value whereas direct addressing uses the operand as a memory address" would suffice.

It seems quite common for students to believe an immediately addressed operand can only be an integer value. Whilst this could possibly be inferred from the instruction set used by AQA in programming questions, it would be beneficial for students' wider knowledge for them to understand the operand could refer to any binary data of any form.

## Q7.

This question was based around the processing of instructions. The majority of students correctly identified operand as the answers to part (a). Part (b)(i) was looking at the fetch part of the fetch execute cycle and a lot of students secured full marks for identifying the values that would be in the registers. A group of students put the answer 0002 into the PC and had not spotted that the question asked for the answer to be written in binary.

Part (b)(ii) asked students to discuss the decode and execute stages. Good answers pointed out the need for the control unit to decode the instruction. Answers that implied that the CIR did the decoding itself were not credited as the CIR is only a register. Students who then identified that a certain part of the processor did the executing secured a mark and a mark was also awarded to those that discussed the role of the ALU.

There was confusion from some students as to the role of the ALU and the accumulator. Students who identified that the status register would be updated picked up a mark.

#### Q8.

- (a) The content of this part has appeared in a similar format in a previous paper and a third of students achieved 2 or 3 marks for this question part. Candidates who secured marks could clearly distinguish what performance changes would occur in a way that was precise and tied in to how a computer works. Answers such as 'the computer would be faster' did not gain a mark when thinking about increasing the clock speed as this does not contain the depth that is expected from an AS-level candidate. Discussing how more instructions would be executed per unit time did secure the mark. Candidates also seemed confused over the address bus with answers along the lines of being able to get more memory addresses per unit time rather than discussing that an increase in the width of the address bus would lead to the CPU being able to access more addressable memory locations.

- (b) This part was based around I/ O controllers, which is an area of the specification that has not been asked about previously. It was obvious that candidates did struggle with this part and this could be due to it being a topic that has not actually been taught or a topic that has only been covered very briefly.

- (i) A lot of candidates could describe what a peripheral was and secured the mark for this section. Candidates who talked about a component outside of the processor did not secure the mark as this could also include main memory which is not considered to be a peripheral.

- (ii) A group of candidates could discuss the role of the I / O port in terms of allowing data to be transferred from the peripheral to the CPU. Others talked about allowing communication between peripheral and CPU and this also secured the mark.

- (iii) As this topic proved to be hard not many candidates could describe another part of the I / O controller. Those that could generally talked about electronics allowing the connection to the system bus or considered the electronics necessary to connect the peripheral to an actual physical port.

- (iv) In this part was a question that candidates attempted and many successfully secured marks. A popular reason, that was allowed for a mark, was the idea that it might slow down the processor. It was pleasing to see stronger candidates talk about the idea of a peripheral operating at a slower speed than the processor and some talked about the need for a buffer. The idea of a peripheral working at a different voltage to the processor was another popular reason that secured a mark.

### Q9.

Last year the long answer question was based around the fetch execute cycle and this question covered a similar topic.

Nearly 80% of students gained all of the marks for part (a) and could correctly provide two registers that would be used in the fetch part of the cycle. Students who failed to secure marks often gave answers such as 'memory bus register' or just 'memory register' and perhaps did not recognise that they could have used the acronyms provided in the figure of part (b).

Part (b) proved to be harder than expected and the common problem was that answers failed to be precise enough to gain marks. When using register notation, marks were not

awarded for answers such as MAR ← PC. The PC part needed to be written as [PC] as this indicates 'the contents of the program counter'. Students who provided written answers commonly indicated that registers actually 'moved' or 'fetched'. Answers such as 'the memory address register fetches.....' or 'the program counter passes...' are not accepted as credit worthy and students should remember that registers are only temporary holders of data. Another common mistake was the idea that the program counter holds instructions rather than the correct concept of it holding a memory address.

For the second mark the question was looking for the idea of an area in main memory being addressed and the contents of this location being passed back to the MBR. A

common answer was just MBR  $\leftarrow$  [MAR] which does not include actually going out to main memory. The majority of students secured at least one mark for question part (b) but it was not common for a student to secure full marks.

## Q10.